Новое поступление

Бесплатная доставка новинка 100% искусственная кожа + PY500 высокотемпературный

Новинка 100% Φ DMSE 020 DMSH Индуктивный Магнитный|Датчик ABS| |

Датчик температуры и влажности Модуль HSU 07J5 аналоговый выход|Датчик ABS| |

Передний левый или правый датчик скорости колес ABS для CITROEN C6 PEUGEOT 407 6D SW Coupe и т. д.

Полупроводниковая очистка разряженная гравировка оптический оптоволоконный

Высокое качество Новый ABS Датчик скорости колеса Передний левый и правый 7700429113

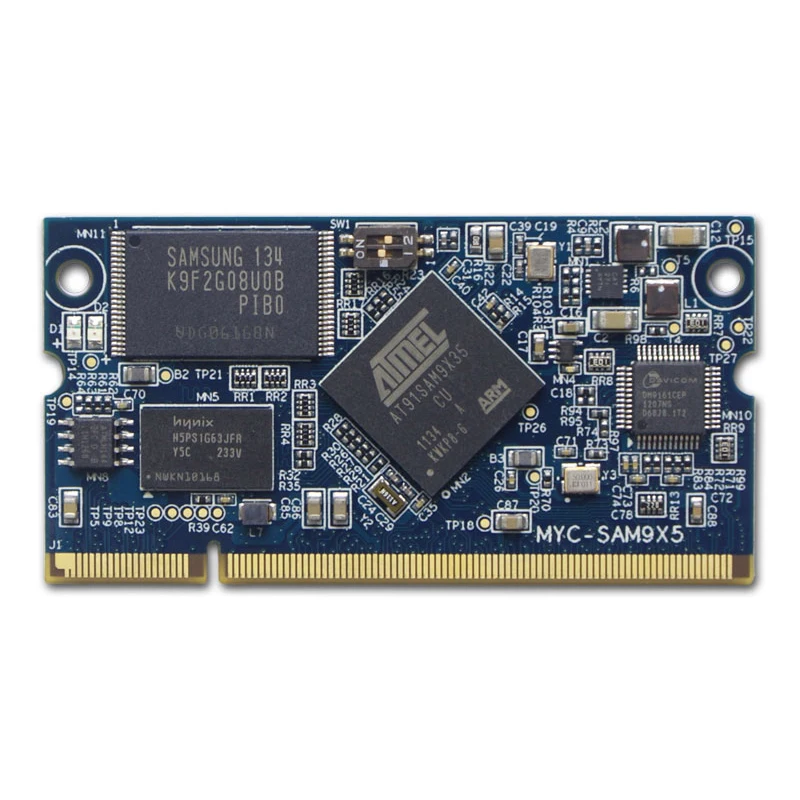

MYC SAM9X5 Core Board SAM9X25 SAM9X35 9X25/9X35 макетная плата|Датчик ABS| |

BETTERSHENGSUN Store

Магазина BETTERSHENGSUN Store работает с 30.05.2019. его рейтинг составлет 83.01 баллов из 100. В избранное добавили 1724 покупателя. Средний рейтинг торваров продавца 4.3 в продаже представленно 25593 наименований товаров, успешно доставлено 2213 заказов. 836 покупателей оставили отзывы о продавце.

Характеристики

Плата DSP2812 + FPGA NIOS TMS320F2812 EP2C8Q208C8|Датчик ABS| |

История изменения цены

*Текущая стоимость 8 178,45 уже могла изменится. Что бы узнать актуальную цену и проверить наличие товара, нажмите "Добавить в корзину"

| Месяц | Минимальная цена | Макс. стоимость | Цена |

|---|---|---|---|

| Apr-06-2026 | 9732.31 руб. | 10219.18 руб. | 9975.5 руб. |

| Mar-06-2026 | 9650.8 руб. | 10133.35 руб. | 9891.5 руб. |

| Feb-06-2026 | 8096.32 руб. | 8501.69 руб. | 8298.5 руб. |

| Jan-06-2026 | 9486.56 руб. | 9960.33 руб. | 9723 руб. |

| Dec-06-2025 | 8260.4 руб. | 8673.37 руб. | 8466.5 руб. |

| Nov-06-2025 | 9323.93 руб. | 9789.49 руб. | 9556 руб. |

| Oct-06-2025 | 9241.31 руб. | 9703.58 руб. | 9472 руб. |

| Sep-06-2025 | 9159.92 руб. | 9617.23 руб. | 9388 руб. |

| Aug-06-2025 | 9078.79 руб. | 9532.0 руб. | 9305 руб. |

Описание товара

[Введение системы]

Этот набор основан на TMS320F2812 + ep2c8q208c8 DSP + FPGA + NIOS обучающей и развивающей платформе, давая полную игру гибкости и мощных функций TMS320F2812 и ALTERA CYCLONE II. Руководство пользователя по разработке набора детально и легко понять, большое количество исходного кода легко начать (разделено на DSP И FPGA 2 части). Мы предоставляем полное ip-ядро FPGA для пользователя, система распределена и подключена через ядро IP, и пользователь может отрезать или добавить функцию в соответствии с потребностями. Поскольку наши периферийные устройства являются передовыми технологиями, такими как FPGA и DSP соединение, преобразование уровня, изоляция шины и разбирательство, это очень удобно, гибко, лаконично, из-за этой системы структуры, таким образом, он работает и является стабильным, и может регулировать ток вождения, задержку, Стандарт выходного уровня каждого порта ввода/вывода в соответствии с требованиями. Он может полностью использовать большое количество ip-ядер CycloneII и PLL для высокоскоростных, высоких стабильных DSP + FPGA приложений, И также может использовать ALTERA DSP builder для создания одного или нескольких ip-ядер DSP, так что может быть создана прикладная система многоядерного процессора. Эти ресурсы не доступны общим CPLD. Эта структура обеспечивает полную гибкость FPGA, высокую производительность и богатые ресурсы TMS320F2812. Совет по разработке через профессионального старшего инженера в соответствии с высокочастотной системой проводки для ручной конструкции проводки, полного рассмотрения системы защиты от помех и петель проблем, поэтому работа и стабильность. Это первый выбор для начинающих и исследователей, занимающихся исследованием F2812 и FPGA.

Эта развивающая доска предназначена для начинающих, чтобы учиться и использовать. Он также может быть встроен в продукт пользователя в качестве системной платы для пользователей, чтобы сделать две разработки, чтобы сократить цикл разработки продукта.

[Системные ресурсы]

DSP процессор TMS320F2812, 32 bit с точечной высокоскоростной цифровой процессор, максимальная рабочая частота 150 м;

Встроенная вспышка 128K * 16 bit в чипе может использоваться для удобного закрепления пользовательских программ, а вспышка может быть зашифрована.

18K * 16 бит SRAM встроен в пленку.

4K * 16 bit BOOT ROM встроен в чип.

1K * 16 бит OTP ROM встроен в чип.

Расширенный 256K * 16 бит SRAM, IS61LV25616;

Расширьте 512K * 16 bit FLASH, SST39VF800, чтобы облегчить пользователям сжигание больших программ;

Размеры на 2-8 л сегментный цифровой трубок;

8 светодиодный светильник, светоизлучающие трубки, удобная индикация состояния;

9 независимых кнопок вытягиваются.

1 зуммер;

1 RS-232 интерфейс, который может быть подключен к ПК для эксперимента.

1 способ RS-485 интерфейс, удобная сеть пользователей, меры защиты портов;

1 интерфейс CAN2.0, удобный для работы в сети пользователя;

16 входных интерфейсов AD (диапазон ввода от 0 до 3 В), из которых во-первых, во-вторых, можно подключить выход DA для проведения эксперимента проверки, 3, 4 входа плюс ограничитель и усилитель после обработки, диапазон ввода от 0 до 3 В (внимание не должно превышать диапазон!) ;

4 DA выходной интерфейс;

1 интерфейс устройства USB 2, схема является зрелым чипом CY7C68013, обеспечивает готовую прошивку и код примера вызова ПК, может легко общаться с ПК, продолжать разработку двух устройств;

Разъем для наушников может легко реализовать функцию воспроизведения.

Гнездо для микрофона используется для удобной записи.

12864 китайский Графический ЖК-дисплей интерфейс;

1602 персональный ЖК-интерфейс;

1 EEPROM, чип 24LC64, эксперимент передачи данных с IIC автобусом;

Интерфейс управления двигателем постоянного тока, конструкция с защитой от штепсельной вилки;

Шаговый интерфейс управления двигателем, конструкция с защитой от штепсельной вилки;

Интерфейс SPI, удобный для работы в сети;

Все выходные интерфейсы PWM были извлечены, и пользователи могут использовать их в соответствии с конкретными требованиями.

Неэкранированный входной интерфейс источника прерывания для внешнего расширения 2 дорог.

Он может расширить до 5 каналов входного интерфейса источника прерывания, и 1 из них может быть срабатывает клавишами.

До 16 входных и 14 выходных интерфейсов, пользователи могут увеличить и удалить количество расширенного ввода/вывода, изменив ip-ядро FPGA, которое мы предоставляем.

Шина открыта, линия передачи данных, адресная линия, линия управления и специальный функциональный штырь-все это светодиодное, что удобно для пользователей для разработки два раза.

+ 5V, 3,3 V, GND и другие мощности тестовые точки;

Источник питания поставляется непосредственно внешним регулятором напряжения.

Независимый переключатель, блок питания управления, удобное управление;

Четыре фиксированных отверстия удобны для установки и фиксации.

2 цифровых трубки, через интерфейс FPGA и DSP.

8 ввода ключа, через FPGA и цифровых сигнальных процессоров.

Предоставляется входной интерфейс источника прерывания.

Он обеспечивает ручную автоматическую схему сброса для легкой отладки.

Обеспечивает открывание шины, линию передачи данных, адресную линию, линию управления, специальный функциональный контакт, удобное развитие пользователя в два раза.

Звуковой сигнал.

Блок питания может быть выбран перемычкой или интерфейсом USB.

1 независимые реле, каждое реле, как правило, открывается и нормально закрыто, и Электрический шок был изведен для удобства пользователя.

Новый ALTERA cylconeII FPGA EP2C8Q208C8 используется для интерфейса и общения с DSP, а расширение порта ввода/вывода выделяется отдельно.

Логические ячейки: 8256

I/O: 139

Регистры: 8745

Дифференциальные I/O пары. 62

Биты памяти: 165888

M4K RAM блоки: 36

Класс скорости: 8

Plls: 2

Чип конфигурации FPGA EPCS16 16 16M может удовлетворить большинство требований к конфигурации.

Память SDRAM 8M x16 bit 16M байт позволяет сохранять собранные временные данные. Или для хранения данных в эксперименте NIOS.

[Вспомогательная информация и программное обеспечение]

1. Полная схематическая схема (формат PDF, гарантированно совпадают с PCB), быстро захватывает Применение ряда практичных интерфейсов.

2. Все эксперименты содержат исходный код языка C и имеют подробные китайские аннотации.

3. Методы и инструменты онлайн-вспышки для закрепления собственной программы пользователя;

4. Руководство по чипу: предоставление информации о чипе на всех чипах на плате разработки;

5. Отправьте оригинальную среду разработки TI DSP CCS3.3;

6. Предоставляем драйвер эмулятора и другие книги DSP и CD-ROM обучающие материалы.

7. Дать Acrobat reader, Bushound USB автобус мониторинга программного обеспечения, Sscom серийный помощник отладки и другие инструменты отладки.

8. Чтобы отправить линейную схему загрузки Altera;

9. Дайте жидкий кристалл шрифт программного обеспечения;

10. Предоставить TCP/IP объем соглашения: Том 1 ~ 3;

11. Предоставьте документы по спецификации USB;

12. Предоставьте CAN2.0 документы спецификации;

13. Предоставьте вам описание системы диска;

14. Предоставить системную документацию FAT16, FAT32;

15. Дайте UCOS-II источник трансплантации на F2812;

16. Дать FFT, FIR и другие библиотеки расчета;

17. Посылка с полным чипом TI.

18. Руководство пользователя: Очень подробное описание, включая анализ цепи, введение кода, руководство по быстрому запуску CCS2000 и т. д.

QUARTUS 8,0 + NIOS II IDE development environment полностью треснутая версия.

Обычная коллекция VHDL

Обучающие материалы VHDL

135 чехлов VERILOG

VERILOG учебники

Обучающие программы DSPbuilder

Отправка программного обеспечения последовательного прослушивателя для разработки RS232

Программное обеспечение извлечения шрифта и разработка программы ЖК-дисплея

USB2.0 главная компьютерная программа и ее исходный код

Полные системные ресурсы FPGA выделяют ip-ядро и исходный код.

Большое количество полных обучающих программ NIOS development. В том числе DSP, EDA, SOPC видео-учебники. Позвольте вам легко освоить DSP, FPGA, SOPC системную разработку.

Вышеуказанная информация предназначена только для изучения, а не для коммерческого использования.

Скачать руководство по экспериментам! (Нажмите правую кнопку, чтобы сохранить его)

[Код и соответствующие эксперименты]

ПК конец демонстрационный код

Язык программирования конечного кода ПК обеспечивает графический интерфейс для Borland C + Builder. Вызывая функцию библиотеки DLL, пользователь продемонстрировал, как получать и получать данные USB. Тот же конечный код DSP также демонстрирует, как читать и записывать данные. Пользователь может обратиться к этому примеру вызова, чтобы быстро завершить разработку своей собственной программы без использования. Позаботьтесь о деталях протокола USB.

USB2.0 верхняя компьютерная передача данных эксперимент управления (предоставление верхнего компьютерного исходного кода, что позволяет легко инвестировать в разработку и применение системы)

Полный драйвер FPGA IP и его исходный код

Полная системная логическая интеграция и распределение ресурсов системы, пользователи могут собирать в соответствии с их собственными потребностями и их приложениями, поэтому системные ресурсы, подключенные к FPGA, имеют соответствующие адреса чтения и записи, И обеспечить полный SDRAM IP ядро, пользователи могут использовать для большой емкости системы хранения данных, Компания также предоставит пользователям систему. Для более высокого качества и недорогого высокоскоростного расширения AD/DA, TFT LCD расширения, оптопара изоляции большого тока ввода/вывода модуля, пожалуйста, обратите внимание на веб-сайт Wah Sheng EDA.

FPGA часть:

(Принимает код VHDL и предоставляет стандартную коллекцию VHDL, более 700 обычно используемых процедур. VERILOG обычные 135 случаев, большое количество сжатого развития и обучающих материалов, как увидеть не может закончить! Для справки пользователей.

Будут запущены дополнительные Экспериментальные и видеообучающие программы. Пожалуйста, обратите внимание на веб-сайт Hua Sheng EDA.

[Стандартная конфигурация]

1. Плата разработки DSP 2812

2, 5V/1A переключатель источника питания

3, кабель USB2.0 1

4, RS232 линия связи 1

5, LCD1602 жидкий кристалл 1

6. 1 двигатель постоянного тока

7. 1 DVD CD-ROM

[Введение системы]

Этот набор основан на TMS320F2812 + ep2c8q208c8 DSP + FPGA + NIOS обучающей и развивающей платформе, давая полную игру гибкости и мощных функций TMS320F2812 и ALTERA CYCLONE II. Руководство пользователя по разработке набора детально и легко понять, большое количество исходного кода легко начать (разделено на DSP И FPGA 2 части). Мы предоставляем полное ip-ядро FPGA для пользователя, система распределена и подключена через ядро IP, и пользователь может отрезать или добавить функцию в соответствии с потребностями. Поскольку наши периферийные устройства являются передовыми технологиями, такими как FPGA и DSP соединение, преобразование уровня, изоляция шины и разбирательство, это очень удобно, гибко, лаконично, из-за этой системы структуры, таким образом, он работает и является стабильным, и может регулировать ток вождения, задержку, Стандарт выходного уровня каждого порта ввода/вывода в соответствии с требованиями. Он может полностью использовать большое количество ip-ядер CycloneII и PLL для высокоскоростных, высоких стабильных DSP + FPGA приложений, И также может использовать ALTERA DSP builder для создания одного или нескольких ip-ядер DSP, так что может быть создана прикладная система многоядерного процессора. Эти ресурсы не доступны общим CPLD. Эта структура обеспечивает полную гибкость FPGA, высокую производительность и богатые ресурсы TMS320F2812. Совет по разработке через профессионального старшего инженера в соответствии с высокочастотной системой проводки для ручной конструкции проводки, полного рассмотрения системы защиты от помех и петель проблем, поэтому работа и стабильность. Это первый выбор для начинающих и исследователей, занимающихся исследованием F2812 и FPGA.

Эта развивающая доска предназначена для начинающих, чтобы учиться и использовать. Он также может быть встроен в продукт пользователя в качестве системной платы для пользователей, чтобы сделать две разработки, чтобы сократить цикл разработки продукта.

[Системные ресурсы]

DSP процессор TMS320F2812, 32 bit с точечной высокоскоростной цифровой процессор, максимальная рабочая частота 150 м;

Встроенная вспышка 128K * 16 bit в чипе может использоваться для удобного закрепления пользовательских программ, а вспышка может быть зашифрована.

18K * 16 бит SRAM встроен в пленку.

4K * 16 bit BOOT ROM встроен в чип.

1K * 16 бит OTP ROM встроен в чип.

Расширенный 256K * 16 бит SRAM, IS61LV25616;

Расширьте 512K * 16 bit FLASH, SST39VF800, чтобы облегчить пользователям сжигание больших программ;

Размеры на 2-8 л сегментный цифровой трубок;

8 светодиодный светильник, светоизлучающие трубки, удобная индикация состояния;

9 независимых кнопок вытягиваются.

1 зуммер;

1 RS-232 интерфейс, который может быть подключен к ПК для эксперимента.

1 способ RS-485 интерфейс, удобная сеть пользователей, меры защиты портов;

1 интерфейс CAN2.0, удобный для работы в сети пользователя;

16 входных интерфейсов AD (диапазон ввода от 0 до 3 В), из которых во-первых, во-вторых, можно подключить выход DA для проведения эксперимента проверки, 3, 4 входа плюс ограничитель и усилитель после обработки, диапазон ввода от 0 до 3 В (внимание не должно превышать диапазон!) ;

4 DA выходной интерфейс;

1 интерфейс устройства USB 2, схема является зрелым чипом CY7C68013, обеспечивает готовую прошивку и код примера вызова ПК, может легко общаться с ПК, продолжать разработку двух устройств;

Разъем для наушников может легко реализовать функцию воспроизведения.

Гнездо для микрофона используется для удобной записи.

12864 китайский Графический ЖК-дисплей интерфейс;

1602 персональный ЖК-интерфейс;

1 EEPROM, чип 24LC64, эксперимент передачи данных с IIC автобусом;

Интерфейс управления двигателем постоянного тока, конструкция с защитой от штепсельной вилки;

Шаговый интерфейс управления двигателем, конструкция с защитой от штепсельной вилки;

Интерфейс SPI, удобный для работы в сети;

Все выходные интерфейсы PWM были извлечены, и пользователи могут использовать их в соответствии с конкретными требованиями.

Неэкранированный входной интерфейс источника прерывания для внешнего расширения 2 дорог.

Он может расширить до 5 каналов входного интерфейса источника прерывания, и 1 из них может быть срабатывает клавишами.

До 16 входных и 14 выходных интерфейсов, пользователи могут увеличить и удалить количество расширенного ввода/вывода, изменив ip-ядро FPGA, которое мы предоставляем.

Шина открыта, линия передачи данных, адресная линия, линия управления и специальный функциональный штырь-все это светодиодное, что удобно для пользователей для разработки два раза.

+ 5V, 3,3 V, GND и другие мощности тестовые точки;

Источник питания поставляется непосредственно внешним регулятором напряжения.

Независимый переключатель, блок питания управления, удобное управление;

Четыре фиксированных отверстия удобны для установки и фиксации.

2 цифровых трубки, через интерфейс FPGA и DSP.

8 ввода ключа, через FPGA и цифровых сигнальных процессоров.

Предоставляется входной интерфейс источника прерывания.

Он обеспечивает ручную автоматическую схему сброса для легкой отладки.

Обеспечивает открывание шины, линию передачи данных, адресную линию, линию управления, специальный функциональный контакт, удобное развитие пользователя в два раза.

Звуковой сигнал.

Блок питания может быть выбран перемычкой или интерфейсом USB.

1 независимые реле, каждое реле, как правило, открывается и нормально закрыто, и Электрический шок был изведен для удобства пользователя.

Новый ALTERA cylconeII FPGA EP2C8Q208C8 используется для интерфейса и общения с DSP, а расширение порта ввода/вывода выделяется отдельно.

Логические ячейки: 8256

I/O: 139

Регистры: 8745

Дифференциальные I/O пары. 62

Биты памяти: 165888

M4K RAM блоки: 36

Класс скорости: 8

Plls: 2

Чип конфигурации FPGA EPCS16 16 16M может удовлетворить большинство требований к конфигурации.

Память SDRAM 8M x16 bit 16M байт позволяет сохранять собранные временные данные. Или для хранения данных в эксперименте NIOS.

[Вспомогательная информация и программное обеспечение]

1. Полная схематическая схема (формат PDF, гарантированно совпадают с PCB), быстро захватывает Применение ряда практичных интерфейсов.

2. Все эксперименты содержат исходный код языка C и имеют подробные китайские аннотации.

3. Методы и инструменты онлайн-вспышки для закрепления собственной программы пользователя;

4. Руководство по чипу: предоставление информации о чипе на всех чипах на плате разработки;

5. Отправьте оригинальную среду разработки TI DSP CCS3.3;

6. Предоставляем драйвер эмулятора и другие книги DSP и CD-ROM обучающие материалы.

7. Дать Acrobat reader, Bushound USB автобус мониторинга программного обеспечения, Sscom серийный помощник отладки и другие инструменты отладки.

8. Чтобы отправить линейную схему загрузки Altera;

9. Дайте жидкий кристалл шрифт программного обеспечения;

10. Предоставить TCP/IP объем соглашения: Том 1 ~ 3;

11. Предоставьте документы по спецификации USB;

12. Предоставьте CAN2.0 документы спецификации;

13. Предоставьте вам описание системы диска;

14. Предоставить системную документацию FAT16, FAT32;

15. Дайте UCOS-II источник трансплантации на F2812;

16. Дать FFT, FIR и другие библиотеки расчета;

17. Посылка с полным чипом TI.

18. Руководство пользователя: Очень подробное описание, включая анализ цепи, введение кода, руководство по быстрому запуску CCS2000 и т. д.

QUARTUS 8,0 + NIOS II IDE development environment полностью треснутая версия.

Обычная коллекция VHDL

Обучающие материалы VHDL

135 чехлов VERILOG

VERILOG учебники

Обучающие программы DSPbuilder

Отправка программного обеспечения последовательного прослушивателя для разработки RS232

Программное обеспечение извлечения шрифта и разработка программы ЖК-дисплея

USB2.0 главная компьютерная программа и ее исходный код

Полные системные ресурсы FPGA выделяют ip-ядро и исходный код.

Большое количество полных обучающих программ NIOS development. В том числе DSP, EDA, SOPC видео-учебники. Позвольте вам легко освоить DSP, FPGA, SOPC системную разработку.

Вышеуказанная информация предназначена только для изучения, а не для коммерческого использования.

Скачать руководство по экспериментам! (Нажмите правую кнопку, чтобы сохранить его)

[Код и соответствующие эксперименты]

ПК конец демонстрационный код

Язык программирования конечного кода ПК обеспечивает графический интерфейс для Borland C + Builder. Вызывая функцию библиотеки DLL, пользователь продемонстрировал, как получать и получать данные USB. Тот же конечный код DSP также демонстрирует, как читать и записывать данные. Пользователь может обратиться к этому примеру вызова, чтобы быстро завершить разработку своей собственной программы без использования. Позаботьтесь о деталях протокола USB.

USB2.0 верхняя компьютерная передача данных эксперимент управления (предоставление верхнего компьютерного исходного кода, что позволяет легко инвестировать в разработку и применение системы)

Полный драйвер FPGA IP и его исходный код

Полная системная логическая интеграция и распределение ресурсов системы, пользователи могут собирать в соответствии с их собственными потребностями и их приложениями, поэтому системные ресурсы, подключенные к FPGA, имеют соответствующие адреса чтения и записи, И обеспечить полный SDRAM IP ядро, пользователи могут использовать для большой емкости системы хранения данных, Компания также предоставит пользователям систему. Для более высокого качества и недорогого высокоскоростного расширения AD/DA, TFT LCD расширения, оптопара изоляции большого тока ввода/вывода модуля, пожалуйста, обратите внимание на веб-сайт Wah Sheng EDA.

FPGA часть:

(Принимает код VHDL и предоставляет стандартную коллекцию VHDL, более 700 обычно используемых процедур. VERILOG обычные 135 случаев, большое количество сжатого развития и обучающих материалов, как увидеть не может закончить! Для справки пользователей.

Будут запущены дополнительные Экспериментальные и видеообучающие программы. Пожалуйста, обратите внимание на веб-сайт Hua Sheng EDA.

[Стандартная конфигурация]

1. Плата разработки DSP 2812

2, 5V/1A переключатель источника питания

3, кабель USB2.0 1

4, RS232 линия связи 1

5, LCD1602 жидкий кристалл 1

6. 1 двигатель постоянного тока

7. 1 DVD CD-ROM

Смотрите так же другие товары: